ASML dự định triển khai rộng rãi công nghệ High‑NA EUV ngay trong năm tới để sản xuất chip với kích thước transistor 1,4 nm và nhỏ hơn.

Tóm tắt ngắn gọn

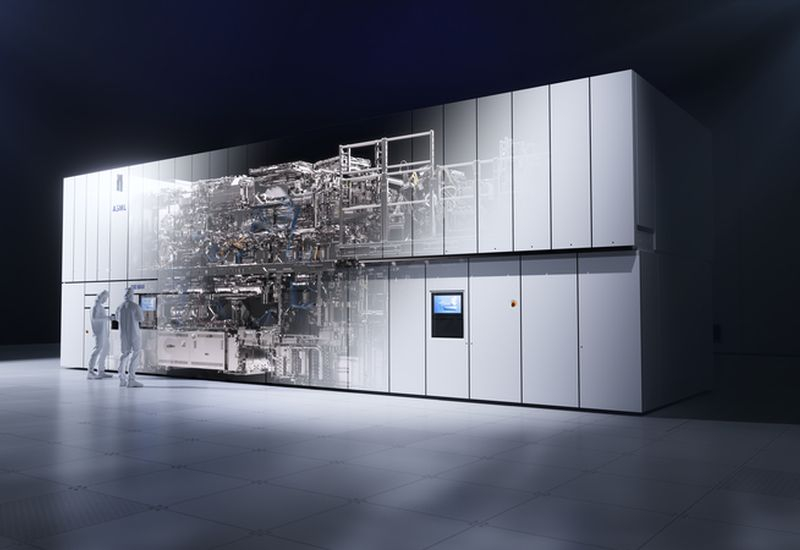

Giai đoạn mới của việc làm nhỏ hạt vi mạch đòi hỏi chuyển sang các phương pháp lithography tiên tiến hơn. Trong hai năm tới, ngành công nghiệp dự kiến sẽ khởi động sản xuất chip sử dụng thiết bị lớp High‑NA EUV, cho phép đạt kích thước lên đến 8 nm trong một lần quét và mở đường cho quy trình công nghệ 1,4 nm và dưới 10 nm (DRAM).

1. Khả năng công nghệ của High‑NA EUV

Tham số Giá trị Độ mở kính (NA) 0,55 Kích thước tối thiểu trong một lần quét ≤ 8 nm Quy trình công nghệ có thể 1,4 nm (vi mạch tích hợp), < 10 nm (DRAM)

Những đặc tính này làm cho thiết bị ASML Twinscan EXE:5200B và các giải pháp tương tự trở nên quan trọng đối với các công nghệ vi điện tử trong tương lai.

2. Các nhân vật chủ chốt

Công ty Trạng thái triển khai Ghi chú ASML Nhà sản xuất High‑NA EUV Khách hàng đầu tiên: Intel, Samsung, SK Hynix TSMC Chưa sẵn sàng cho sử dụng đại trà Giá trị một hệ thống – 380 triệu USD; dự kiến sẽ từ bỏ chip 1,4 nm Intel Vào tháng 12 năm 2023 giới thiệu Twinscan EXE:5200B Chuẩn bị ra mắt công nghệ 14A và thiết bị đi kèm Samsung Electronics Nhận được máy quét đầu tiên vào tháng 12 năm 2023; thứ hai – trong nửa năm này Kế hoạch sử dụng cho Exynos 2600 (2 nm) và các bộ xử lý Tesla tương lai SK Hynix Thành thạo High‑NA EUV từ tháng 9/2023 Đã áp dụng lithography EUV thông thường trong DRAM (10 nm), dự định sử dụng tối thiểu năm lớp EUV cho thế hệ thứ sáu Micron Technology Chưa xác định thời gian triển khai Có thể có kế hoạch về High‑NA EUV Rapidus (Nhật Bản) Thành thạo công nghệ 2 nm; dự kiến 1,4 nm vào 2029 Đến năm 2027 sẽ khởi động sản xuất đại trà chip 2 nm tại Hokkaido

3. Các khía cạnh kinh tế

* Giá trị thiết bị – một hệ thống High‑NA EUV khoảng 380 triệu USD.

* Chuyển sang thiết bị đắt hơn làm tăng chi phí sản xuất, cuối cùng phản ánh lên người tiêu dùng.

* Do đó các nhà sản xuất lớn (TSMC, Rapidus) cẩn trọng và dự định triển khai theo từng giai đoạn.

4. Thời gian dự kiến

Các máy quét lithography mới của ASML dành cho sản xuất đại trà sản phẩm bán dẫn tiên tiến sẽ được áp dụng tích cực từ năm 2027–2028. Cho đến khi đó, các công ty sẽ dần điều chỉnh dây chuyền sản xuất của mình, tích hợp High‑NA EUV vào quy trình công nghệ hiện có.

Kết luận

Chuyển sang High‑NA EUV là bước quan trọng để đạt được kích thước 1,4 nm và DRAM nhỏ gọn hơn. Các nhà chơi lớn thế giới đã bắt đầu các công tác chuẩn bị, nhưng triển khai đại trà dự kiến chỉ xảy ra sau vài năm do chi phí cao và nhu cầu thích ứng chuỗi sản xuất.

Asted Cloud

Asted Cloud

Bình luận (0)

Chia sẻ ý kiến của bạn — vui lòng lịch sự và đúng chủ đề.

Đăng nhập để bình luận