Công cụ mới sẽ tăng tốc quá trình tìm kiếm lỗi trong transistor nanomet, làm cho việc gỡ lỗi các quy trình công nghệ trở nên dễ dàng và thú vị hơn

Cách mới để nhìn thấy các khuyết tật nguyên tử trong các bán dẫn hiện đại

Các nhà khoa học từ Đại học Cornell cùng với các công ty ASM và TSMC đã tạo ra một phương pháp cho phép trực quan hóa những sai lệch nguyên tử ẩn trong chip tiên tiến. Cách tiếp cận này đặc biệt quan trọng cho việc gỡ lỗi quy trình sản xuất vi mạch: càng chính xác hơn đánh giá được khuyết tật, thì tỷ lệ thải giảm và quá trình đạt tới mức trưởng thành nhanh hơn.

Nội dung nghiên cứu

Trong công trình này, các mẫu đã được xử lý với transistor Gate‑All‑Around (GAA) – loại van mới nhất bao phủ toàn bộ kênh. Trung tâm Imec tại Bỉ cung cấp các mẫu. Mỗi kênh GAA là một “ống” gồm 18 nguyên tử theo đường cắt ngang; tường của nó có thể có sự không đồng đều, vết nứt và các khuyết tật khác ảnh hưởng trực tiếp đến đặc tính transistor. Dù sau khi xử lý không thể thay đổi cấu trúc, các nhà nghiên cứu đã có thể theo dõi chất lượng chế tạo ở mỗi giai đoạn của hàng nghìn bước sản xuất, nhằm giảm số lỗi.

Cách họ thực hiện

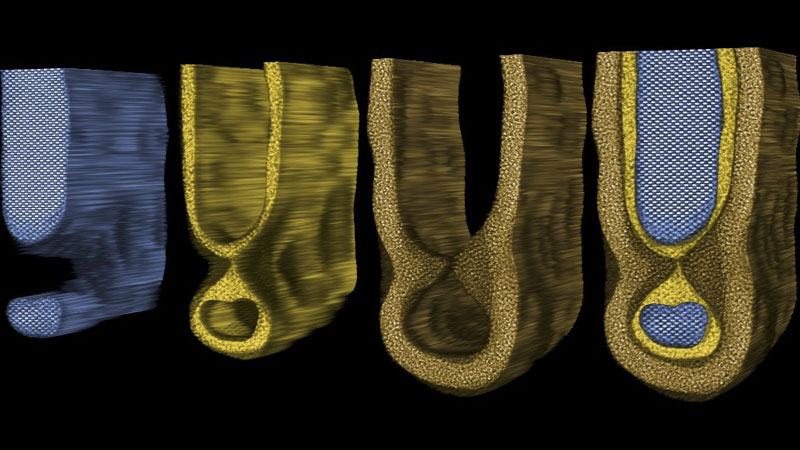

Để quan sát các khuyết tật có kích thước vài nguyên tử, các nhà khoa học đã sử dụng kỹ thuật electron ptychography đa mặt phẳng (multislice electron ptychography). Đây là phương pháp có độ phân giải sâu vật liệu dưới mức angstrom, ở cấp độ nanomet. Nó thu thập sự lan truyền của electron và xây dựng hình ảnh theo quy mô nguyên tử.

Bước quan trọng – thu thập dữ liệu nhiễu sắc 4 chiều qua bộ dò EMPAD trong kính hiển vi điện tử quét xuyên (STEM). Sau đó, dữ liệu được thực hiện tái cấu trúc pha và mô phỏng sự lan truyền electron qua nhiều “đoạn” vật liệu. Khác với các phương pháp chiếu tán truyền thống, ptychography khôi phục toàn bộ cấu trúc thể tích từ một tập hợp đo lường duy nhất, cho phép xác định chính xác vị trí của từng nguyên tử, biến dạng cục bộ của lưới và tham số biên pha.

Lợi ích

- Đánh giá chất lượng và định lượng phổ các khuyết tật – trước đây chỉ có thể được truy cập qua các phương pháp gián tiếp.

- Khả năng nhanh chóng phát hiện và khắc phục các vấn đề công nghệ ở giai đoạn đầu của quá trình thiết kế.

- Sự quan tâm đã được xác nhận từ các nhà chơi lớn như TSMC, chứng minh giá trị thực tiễn của phương pháp trong việc gỡ lỗi sản xuất chip hiện đại.

Như vậy, phương pháp mới mở ra con đường tới kiểm soát chất lượng đáng tin cậy và hiệu quả hơn trong lĩnh vực sản xuất vi mạch công nghệ cao.

Asted Cloud

Asted Cloud

Bình luận (0)

Chia sẻ ý kiến của bạn — vui lòng lịch sự và đúng chủ đề.

Đăng nhập để bình luận